# GLOBAL JOURNAL OF ENGINEERING SCIENCE AND RESEARCHES ENERGY SAVING TECHNIQUES FOR JOINT HYBRID FREQUENT VALUE CACHE AND MULTI-CODING IN DATA BUS

Katheragandla Vamsi Krishna<sup>\*1</sup> & Shavali<sup>2</sup>

<sup>\*1</sup>PG Scholar, Ece, SVIST College of Engineering, Kadapa, AP, India <sup>2</sup>Associate Professor, ECE, SVIST College of Engineering, Kadapa, AP, India

## ABSTRACT

In the profound submicron innovation area, the on chip buses devour extensive measure of aggregate energy of inserted multi-center chip. Loads of methods have been created to lessen the bus energy utilization. FVE (Frequent Value Encoding) and FV-MSB (Frequent Value-Most Significant Bit) which abuse rich esteem territory on the information buss, are powerful strategies for diminishing information bus energy utilization. In this paper, we propose a technique that adventures more esteem area that is neglected by the FVE and FV-MSB. We found that a lot of non-visit esteems and low-arrange bits of fractional successive qualities, not caught by the FVE and FVMSB, created extensive number of switching action. Subsequently, we deliver a bus energy sparing strategy in view of incessant qualities and multi-coding which can be utilized to additionally diminish the on-chip information bus switching action.

# I. INTRODUCTION

Energy utilization is one of the significant viewpoints in the outline of on-chip multi-center circuits. With the consistent scaling of silicon innovation, region and power utilization of interconnects are one of the principle bottlenecks for on-chip bus. As the innovation of deep submicron (DSM) innovation, the on-chip bus disperses a critical portion of the aggregate framework control spending plan [1]. Thus, the plan of intensity effective information bus is today perceived as a key issue, particularly for the implanted multi-center on-chip framework. In the ongoing past, the encoding ideal models for diminishing the bus energy utilization have been researched. Frequent value encoding(FVE), which makes utilization of the esteem region, is an effective technique for information bus energy sparing. Yang Jun et al. utilized disconnected advancement calculation and dynamic discovery of continuous incentive for enhancement of off-chip bus energy utilization [2]. In any case, this strategy had a few imperfections when it was utilized to upgrade the on-chip bus energy utilization. Initially, it isn't viewed as the impact of coupling switching movement (SA), which represents an extensive extent of aggregate SA and prompts expansive number of bus energy utilization in DSM innovation. While considering the impact of the coupling SA on the on-chip information bus dynamic energy utilization, the proficiency of FVE is decreased. Also, this approach requires visit esteem store has a high hit rate, the low hit rate will diminish the effectiveness of energy sparing. Anyway the region is constrained in on-chip outline, which influences the quantity of continuous incentive to store sections is little and the reserve hit rate will be low. In this manner a changed technique ought to be available to enhance the hit rate and productivity of FVE on upgrading information bus energy utilization. With a specific end goal to diminish more off-chip bus dynamic energy utilization, FV-MSB [3] additionally built up the esteem territory and added the MSB store to visit esteem reserve for incomplete regular qualities. The strategy could additionally diminish the SA, which increased more approaches of information bus energy sparing. Be that as it may, FV-MSB still has a few imperfections in the advancement of on-chip bus energy utilization as takes after: (a) Limited on-chip territory decides the extent of the successive esteem store ought to be little thus the reserving FV number was little, which lessened the hit rate of the continuous esteem store and debilitated the productivity of bus energy sparing; (b) The low request bits of the fractional incessant qualities (put away in the MSB store) and the non-visit esteems created substantial number of SA and were not treated with; (c) The impact of coupling SA on bus energy utilization was not considered. The above imperfections made the productivity of FV-MSB unimportant on enhancing the on-chip information bus energy utilization. The protest of this paper is the on-chip information bus with 70nm innovation, in which the impact of coupling SA can't be overlooked. So the above techniques can't acquire the coveted impact on the upgrading bus dynamic energy utilization. Keeping in mind the end goal to accomplish the improvement objective, this paper introduces a coupling SA-mindful strategy HFVCMC (Hybrid

#### ISSN 2348 – 8034 Impact Factor- 4.022

Frequent Value Cache Multi-Coding) to lessen the on-chip information bus energy utilization, which in view of successive qualities and aggregate SA (the entirety of self-SA and coupling SA) impression of the bus. Other than of utilizing successive qualities, the HFVCMC can see the aggregate SA number of the non-visit esteems and the low request bits of incomplete regular qualities to enhance the bus energy utilization, which can naturally choose the encoding plan to get the base number of aggregate SA and accomplish the most extreme information bus dynamic energy sparing.

# II. BACKGROUND AND RELATED WORK

#### A. Need of Power Management in Main Memory

As of late, the aggregate power utilization of installed frameworks, server farms and supercomputers has fundamentally expanded [12, 13], which has additionally expanded the carbon impression of IT. To address this, PC planners have proposed a few procedures for decreasing the energy utilization of processing frameworks [14, 15]. Since a huge portion (upto 40% of energy spent in server-class frameworks is devoured by the fundamental memory, the strategies for sparing energy in primary memory frameworks are imperative for enhancing energy productivity of registering frameworks. Since PCM has considerably littler spillage energy than DRAM, as of late, there has been a critical enthusiasm for utilization of PCM. PCM has been assessed in setting of GPUs (illustrations handling unit), implanted frameworks, constant frameworks, video applications et cetera. Truth be told, utilization of PCM has likewise been investigated for outlining stores. As the utilization of PCM increments, dealing with its capacity utilization turns out to be significantly more essential.

## B. A Brief Background on Phase Change Memory

We quickly survey the plan of PCM. A PCM cell involves a NMOS get to transistor and a capacity resistor which is made of a chalcogenide amalgam. To store a parallel an incentive on PCM, warm is connected to it which advances the physical condition of the amalgam with specific protections. At the point when the composite is warmed to a high temperature (more prominent than 600 degree Celsius) and immediately chilled off, it advances into a formless substance with high electrical obstruction which speaks to paired "0". Then again, when the composite is warmed to a temperature between the crystallization (300 degree Celsius) and liquefying (600 degree Celsius) focuses and chills off gradually, it takes shape to a physical state with bring down obstruction, which speaks to double "1". The distinction in obstruction esteems between the two conditions of PCM is regularly 3 requests of greatness. PCM recollections accomplish high thickness by misusing this high opposition range to store different bits in a solitary cell, this structure is known as multi-level cell or MLC. PCM is byte-addressable and is resistant to radiation prompted delicate mistakes.

#### C. An Overview of Energy Saving Techniques for PCM

PC planners have proposed a few methods for sparing energy in PCM frameworks. A few analysts have proposed cross breed PCM-DRAM plan [17]. These systems mean to accomplish the best of both DRAM and PCM, viz. the short inertness and high compose perseverance of DRAM and low spillage power and high thickness of PCM. A few systems change over PCM compose task to peruse before-compose (or information examination compose) activity to decrease compose energy [8]. These systems, alluded to as "differential express" based methods, read out the old incentive in the PCM exhibit before composing the better one and contrast them with compose just those bits that need to change. A few specialists propose undertaking planning based strategies to address the difficulties in half breed DRAM-PCM based fundamental memory.

A few different systems depend on decreasing compose activity to PCM memory. A few analysts propose last level store administration methods for enhancing energy productivity of PCM fundamental memory. Different scientists have proposed pressure based methods to decrease compose movement to PCM. A few different systems mean to address the compose inertness issue, and its destructive effect on read dormancy emerging because of bank clashes and endeavor to use compose territory to combine every conceivable change to the information by Musing cradles previously they are at long last kept in touch with PCM. A few wear-leveling methods which work by decreasing the quantity of keeps in touch with PCM additionally for the most part spare compose energy. PCM additionally offers the capacity to store various bits per cell and a few scientists propose methods to accomplish this in a energy

290

ISSN 2348 - 8034 Impact Factor- 4.022

proficient way. At long last, a few analysts have proposed design or gadget level test systems for examining nonunstable recollections, which encourage investigation of PCM.

#### **Existing System**

PC engineers have proposed a few methods for sparing energy in PCM frameworks. A few analysts have proposed half breed PCM-DRAM plan. These procedures intend to accomplish the best of both DRAM and PCM, viz. the short inertness and high compose continuance of DRAM and low spillage power and high thickness of PCM. A few strategies change over PCM compose activity to peruse before-compose (or information examination compose) task to lessen compose energy [8, 10, 57–60]. These methods, alluded to as "differential express" based procedures, read out the old incentive in the PCM exhibit before composing the updated one and contrast them with compose just those bits that need to change. A few scientists propose undertaking booking based procedures to address the difficulties in cross breed DRAM-PCM based fundamental memory.

A few different strategies depend on lessening compose activity to PCM memory. A few analysts propose last level reserve administration strategies for enhancing energy effectiveness of PCM principle memory. Different analysts have proposed pressure based strategies to lessen compose activity to PCM. A few different strategies expect to address the compose idleness issue, and its unsafe effect on read inactivity emerging because of bank clashes and attempt to use compose region to combine every conceivable change to the information by utilizing cushions before they are at long last kept in touch with PCM.

A few wear-leveling strategies which work by diminishing the quantity of keeps in touch with PCM additionally for the most part spare compose energy. PCM likewise offers the capacity to store various bits per cell and a few analysts propose strategies to accomplish this in a energy proficient way. At long last, a few analysts have proposed design or gadget level test systems for contemplating non-unstable recollections , which encourage investigation of PCM.

# III. ENERGY SAVING TECHNIQUES

The read power and postponement of PCM are in an indistinguishable range from that of DRAM, nonetheless, its compose control is altogether higher, which can be a few times that of DRAM. Conversely, for DRAM, both read and compose times are comparable. Keeping in touch with a PCM cell requires high current thickness over a huge timeframe. Henceforth, to guarantee revise activity, hard points of confinement on the quantity of concurrent composes must be authorized which limits compose throughput and general execution. Along these lines, inability to spare compose energy may invalidate the energy sparing preferred standpoint increased because of low spillage intensity of PCM. Further, vast power utilization of PCM can have pernicious impact on its activity. It might prompt abusing power limits, which may thus prompt voltage drops in the power supply or inordinate streams moving through the processor. It might expand the temperature which may additionally build the spillage energy utilization of different parts of the framework. It might likewise make consistent mistakes, inadequate PCM stage changes, PCM read blunders, and so on which may prompt chip disappointments or chip-maturing. Along these lines, control administration of PCM is critical. In this segment, we audit a few methods for overseeing power utilization of PCM. Roughage et al. propose a strategy to decrease compose control utilization of PCM banks. Their strategy depends on the perception that ordinarily just a little segment of the bits (for instance, under 25% by and large) are composed to which expend control. Their method screens the quantity of bits that will change on a compose and henceforth, should be composed. This gives a gauge of the quantity of bits and henceforth, measure of intensity devoured in a compose. At that point, to not surpass the power spending plan, the memory controller issues composes just when there is sufficient capacity to help them.

Cho et al. propose a method named, Flip-N-Write to enhance PCM compose transmission capacity, compose energy, and compose perseverance under a quick compose control imperative. Their strategy takes a shot at the perception that numerous piece keeps in touch with PCM are repetitive. Their procedure replaces a compose task with readchange compose activity to skip composing a bit if the bit being composed is same as the initially put away piece. Further, to limit the greatest number of bits which are composed, they utilize a "flip" piece. On the off chance that

291

DOI: 10.5281/zenodo.1313654

#### ISSN 2348 - 8034 Impact Factor- 4.022

putting away the flipped estimation of information requires less number of bit-compose tasks, their procedure stores the information in flipped frame and changes the flip piece to ON. Utilizing their strategy, the compose transfer speed is multiplied, which likewise enhances the compose continuance and decreases the compose energy.

Lee et al. propose utilizing various column cushions inside a PCM chip, which diminishes the read dormancy and furthermore the compose energy through compose combining. Numerous keeps in touch with a similar area are caught up in the supports, in this way bringing about significantly more modest number of compose backs to the PCM cluster. They likewise propose a method which utilizes various grimy bits in the store squares to empower halfway composes. Utilizing this, the quantity of bit refreshes are decreased by not composing immaculate, clean information partition in a messy reserve square to the fundamental memory when the store square is supplanted. Their strategies additionally increment the lifetime of PCM.

Zhang et al. examine PCM with regards to 3D diestacking. Utilizing diagnostic and circuit-level displaying for PCM portrayal, they demonstrate that the programming intensity of PCM cells can be lessened as the chip temperature is lifted. This high-temperature well disposed task of PCM can be profitably used to plan 3D kick the bucket stacking memory frameworks.

They propose a half breed memory plan where a vast part of PCM is utilized as an essential memory space and a little bit of DRAM is utilized as a compose support to diminish the quantity of keeps in touch with PCM. They likewise propose an OS-level paging plan that considers the memory reference qualities of utilizations and relocates the hot-changed pages from PCM to DRAM with the goal that the existence time corruption of PCM is lightened. Their procedure likewise enhances the energy proficiency of the memory framework.

Ferreira et al. propose a reserve trade approach for sparing PCM fundamental memory energy. Their approach expects to decrease the compose back activity to primary memory. The arrangement is called N-Chance where N can be fluctuated. This approach removes the minimum as of late got to clean page from store, except if the greater part of the N slightest as of late got to pages are grimy, provided that this is true, it expels the minimum as of late got to page. For the situation when N = 1, this strategy turns into the regular LRU (slightest as of late utilized) arrangement. They have demonstrated that for an appropriate decision of N, their approach can be altogether superior to the LRU arrangement.

Hu et al. propose a method for decreasing the quantity of keeps in touch with PCM fundamental memory. Their method depends on information relocation and re-calculation. In an inserted CMP (chip multiprocessor) having scratch-cushion memory, their procedure moves information to the scratch-cushion memory of an alternate center to stay away from compose backs of shared information. In this way, by incidentally putting away the information on scratch-cushion, their strategy lessens the quantity of compose backs. Their strategy utilizes program examination to decide when and where the information ought to be relocated. They additionally propose information re-calculation to diminish the quantity of compose exercises by disposing of the information which ought to have been composed back to the principle memory and recomputing these information when they are required. They display the issue of information movement as a most brief way issue. Additionally, they propose a way to deal with locate the ideal information movement way with negligible cost for both filthy information and clean information.

Qureshi et al. propose a half breed memory outline where PCM memory is expanded with a little DRAM that goes about as a "page reserve" for the PCM memory. The page reserve supports regularly got to pages and in this manner helps execution and enhances PCM perseverance by lessening the quantity of keeps in touch with PCM with compose joining and mixing. Further, at store line level, just the lines adjusted in a page are composed to the fundamental memory. At long last, at square level, swapping is utilized for accomplishing wear-leveling. Their strategy likewise decreases the page issues which enhances the execution of the framework. Notwithstanding, when the applications have poor region, the upside of utilizing page store decreases.

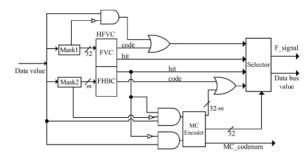

Our encoding strategy is added to multi-center framework as appeared in Fig. 1. There are five HFVCMC modules – one at every one of the centers and one at the L2 end. As indicated by their capacities, HFVCMC module can be separated into two sections: encoding and deciphering. Then again, it is fundamentally made out of HFVC module and MC module from an auxiliary perspective.

HFVC is made out of FVC and FHBC, where the previous is utilized to reserve finish visit esteems and the last is utilized to store m-bit width incomplete incessant qualities (high request bits visit esteems), and both utilize the scontent address memory (CAM). To encourage the hunt, the esteem

for sending should be treated with utilizing a veil to get a similar piece width with the incentive in the HFVC, which is 32-bit esteem requires a 32-bit cover, m-bit esteem requires m-bit veil. With a specific end goal to diminish the equipment multifaceted nature and the energy utilization cost, which are presented by the strategy itself, the qualities and their lists in all the HFVC are the same, and stay unaltered all through the execution. On the off chance that the qualities in the HFVC powerfully in light of execution attributes, by following the incessant qualities amid the run, the circuits will be intricate and bring additional energy cost. Further, settling the qualities can make the circuit significantly more productive from both planning and power points of view, and we subsequently utilize the HFVC as for the most part a query component and fix the qualities from the earlier. We store four qualities in both parts(FVC and FHBC) of each HFVC, individually. The quantity of reserving esteems in each HFVC is dictated by the on-chip constrained region and the scope rate of incessant qualities.

The restricted limit of HFVC compels the quantity of its entrances is little. Along these lines there will be likewise a ton of qualities can't be hit in the HFVC. These qualities contain the nonfrequent esteems and the LOB (low-arrange bits, whose high request bits are put away in FHBC), if don't be treated with, will cause expansive number of SA and deliver extensive bus energy utilization. To additionally decrease the SA caused by these qualities, we present a MC module constituted of four encoding plans: Original, Invert, Odd Invert and Even Invert encodings. For an esteem entering the MC encoder, the encoder figures the aggregate SA remove as indicated by (6) and naturally chooses the encoding plan, which can get the base SA separate, and produce the encoded esteem and coding number to be sent.

In the outline of the technique, we likewise need to decide the quantity of sign lines and the bit-width m of the qualities, which we store in the FHBC. These two issues are talked about as takes after.

1) Indication line. We utilize one piece line to demonstrate the sending esteem is a successive or a non-visit esteem. The control flag F motion on the sign line is 1, showing that the sending esteem is a successive esteem (put away in FVC or FHBC), and F flag is 0, demonstrating a non-visit esteem.

For decreasing circuit multifaceted nature, we shouldn't add an additional line to show a regular esteem originating from FVC or FHBC. To do this, we utilizes the high-arrange bit lines of bus to exchange the list of the continuous incentive at the sender and the collector can judge the incentive from FVC or FHBC by the estimation of the list. So there is just a single additional control line is acquainted with demonstrate an esteem is a continuous esteem or not

293

ISSN 2348 - 8034 Impact Factor- 4.022

#### ISSN 2348 – 8034 Impact Factor- 4.022

and where it is originating from. Two additional control lines are expected to demonstrate the encoding plan of the encoded esteems since four encoding plans are utilized as a part of the MC module. Along these lines, in our strategy three sign lines are acquainted with show the beneficiary accurately managing the encoded esteems.

2) Selecting the measure of m. Instinctively, little estimation of m gets substantial number of hits in the FHBC. Be that as it may, vast number of hits require not really infer a huge lessening in bus SA. In the event that m is bigger, the hit rate will diminish, yet the impact of the hit on SA lessening will increment. To locate the best estimation of m, we directed analyses where we changed m from 2 to 30 with step estimation of 2 as indicated by the general SA diminishments. The outcomes (Fig. 3) demonstrate that the approaches of bus energy sparing can be augmented when m is four. So we make the measure of m rise to four in the accompanying segments of this paper.

#### HFVCMC encoder

We denote Bj is the value to be sent on the n-bit width data bus at cycle j, and it can be expressed as  $Bj = (bjn, bjn-1, bjn-2, \dots, bj1)$ . B(j-1)enc represents the encodedvalue at cycle j-1. Four encoding schemes of MC module are expressed as: Original B(org), Invert B(inv), Odd Invert B(odd), Even Invert B(evn) with the coding number 00, 01, 10, 11, respectively. The encoded value that Bj is directly appended its coding number is defined as Bj(org). The encoded value that all the bits of Bj are inverted then appended its coding number is defined as Bj(odd). The encoded value that the odd bits of Bj are inverted then appended its coding number is defined as Bj(odd). The encoded value that the even bits of Bj are inverted then appended its coding number is defined as Bj(odd). The encoded value that the even bits of Bj are inverted then appended its coding number is defined as Bj(odd). The encoded value that the even bits of Bj are inverted then appended its coding number is defined as Bj(evn). The coding number indicates which encoding scheme is used to encode the sending value. The function ST n(d1, d2) is used to calculate the vertical distance X between the two n-bit width values, the function CT n(data) is used to calculate the horizontal distance Y of n-bit width value, and Md represents the minimum total SA distance of the encoded value. The algorithm for the HFVCMC encoder is described in Algorithm 1. Fig. 4 shows the HFVCMC encoder schematic diagram. The value to be sent is logically AND-ed with the mask in order to get proper value with the same width as the value in HFVC. To reduce the delay, we search the two parts of HFVC in parallel. There would be four results of searching HFVC, discussed as follows.

A hit only in FVC, the index of the value in FVC will be sent instead of the actual value to the following selector.

A hit in FVC and FHBC at the same time, the FVC has higher priority and the index of the value in FVC will be sent instead of the actual value to the following selector, because it can reduce more SA.

3) A hit only in FHBC, the index of high-order bits value in FHBC is sent to the following OR-gate instead of the actual high-order bits, and the low-order bits is sent to the MC encoder. Then the MC encoder calls Algorithm 2 to select the encoding scheme and produce the encoded value and coding number, then the encoded value of the low-order bits is sent to the following OR-gate and the coding number is sent to receiver. In OR-gate, the index of high-order bits is OR-ed with the encoded low-order bits, then the whole encoded value is sent to the following selector.

4) A miss in FVC and FHBC, the value to be sent is directly entered the MC encoder, the encoder calls the Algorithm 2 to select the encoding scheme and produce the encoded value and coding number. Then the encoded value is sent to the following selector and the coding number is sent to receiver.

Finally, the selector determines the encoded value to be sent on the bus and the signal value of F signal. If there is a hit in FVC or FHBC the F signal is set to 1, else is set to 0. Algorithm 2 is MC encoding function algorithm, which selects the encoding scheme with minimum total SA distance according to (6) and returns the encoded data value and its coding number.

DOI: 10.5281/zenodo.1313654

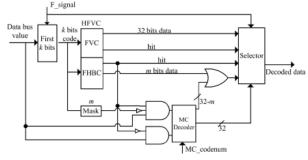

C. HFVCMC decoder

ISSN 2348 - 8034 Impact Factor- 4.022

The algorithm for the HFVCMC decoder is described in Algorithm 3. Fig. 5 shows the HFVCMC decoder schematic diagram. When the value to be sent is a frequent value, the high-order k-bit (k is equal to 3 in this paper for eight values) value of encoded value on the bus is the index in HFVC. When the value to be sent is a non-frequent value, the encoded value occupies all the bit lines of the bus. When the decoder receives an encoded value, it firstly checks the control signal F singal. If F singal is 1, indicating that the received value is a frequent value, the decoder need judge the value coming from FVC or FHBC according to the value on high-order k-bit lines. If the high-order k-bit value corresponding to the index of complete frequent value in FVC, the decoder fetches the original value from FVC with the index. While if the high-order k-bit value corresponding to the index of original value from FHBC, the decoder fetches the high-order bits of original value from FHBC, the decoder fetches the high-order bits according to the coding number MC codenum. Then the two partial value is OR-ed to obtain the original value. If F singal is 0, indicating that the received is a non-frequent value, the decoder directly calls the Algorithm 4 to obtain the original value with the original value with the coding number MC codenum. The above obtained values were firstly sent to selector, then the selector selects the value which has the highest priority as the final actual value. Algorithm 4 is MC decoding function algorithm, which returns the actual value with coding number.

# **IV. CONCLUSION**

We display another technique called HFVCMC to improve the dynamic energy sparing of information bus. We consider two levels, circuit plan and calculation, for bus dynamic energy sparing. In circuit configuration level, we present a crossover visit esteem store, which can enhance the hit rate of FVC, and a MC structure to lessen the bus SA and energy utilization; In calculation level, we introduce four calculations, which can see the SA number and naturally select the encoding plan for limiting the aggregate SA separation and energy utilization of information bus.

#### REFERENCES

- 1. Jafarzadeh, N., Palesi, M., Khademzadeh, A., Afzali-Kusha, A., Data encoding techniques for reducing energy consumption in network-onchip[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22(3):675-685.

- 2. Yang, J., Gupta, R., Zhang, C. J., Frequent value encoding for low power data buses[J]. ACM Transactions on Design Automation of Electronic Systems, 2004, 9(3):354-384.

- 3. [3] Suresh, D. C., Yang, J., Zhang, C. J., Agrawal, B., Najjar, W., FVMSB: a scheme for reducing transition activity on data buses[C], High Performance Computing HiPC 2003. Springer Berlin Heidelberg, 44-54.

- 4. Bishop, B., Bahuman, A., A low-energy adaptive bus coding scheme[C]// IEEE Computer Society Workshop on VLSI 2001, WVLSI 2001:118-122.

- 5. Yang J., Zhang Y. T., Gupta, R., Frequent value compression in data caches[C]// MICRO-33. Proceedings. 33rd Annual IEEE/ACM International Symposium on Microarchitecture, 2000:258-265.

- 6. Peng, Y. R., Ku, B. W., Park, Y., Park, K., Design, packaging, and architectural policy co-optimization for DC power integrity in 3D DRAM[C], Design Automation Conference (DAC), 2015 52nd ACM/EDAC/IEEE. 1-6.

- 7. Wang, S. N., Luo, B., Shi, W. S., Tiwari, D., Application configuration selection for energy-efficient execution on multicore systems[J]. Journal of Parallel and Distributed Computing, 2016, 87(1):43-54.

# 8. Zhao H, Chen M, Qiu M, et al. A novel pre-cache schema for high performance Android system[J]. Future Generation Computer Systems, 2016, 56(C):766-772.

ISSN 2348 - 8034

**Impact Factor- 4.022**

- 9. Stan, M. R., Burleson, W. P., Bus-invert coding for low-power I/O[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 1995, 3(1):49-58.

- 10. Fang, Chia-Hao, Fan, Chih-Peng., Novel low-power bus invert coding methods with crosstalk detector[J]. Journal of the Chinese Institute of Engineers, 2011, 34(1):123-139.

- 11. Kaushik, B. K., Agarwal, D., Babu, N. G., Bus encoder design for reduced crosstalk, power and area in coupled VLSI interconnects[J]. Microelectronics Journal, 2013, 44(9):827-833